静電気放電(ESD)試験

EMC対策集1として、エミッション試験の中でNGとなりやすい「放射電磁妨害(不要輻射)測定」での対策集を記載したので、今回は、イミュニティ/サセプタビリティ試験の中で特にNG対策が必要な静電気放電(ESD)試験を取り上げます。

ESD試験は、静電気を帯電した人体が電子機器に触れた際に生じる静電気放電に対し、耐性が確保できているか確認するための試験です。

実際の試験は、静電気を発生させる静電ガンを用いて、以下の3種類の印加を行います。

[接触放電(直接放電)]

電子機器の金属部分に直接静電ガンを接触させて、静電気を印加します。

(電子機器に金属部分が無い場合は行いません。)

[接触放電(間接放電)]

電子機器の近くに金属板を置き、金属板に直接静電ガンから静電気を印加させ、生じる電磁界の影響による耐性を試験します。

[気中放電]

電子機器の金属部分ではない箇所(樹脂部分など)で、人が触れやすいと想定される箇所に、放電ガンのトリガを引いたまま接触するまで近づけ放電を行う試験です。

それでは、経験した問題と対策を備忘録として以降に記載します。

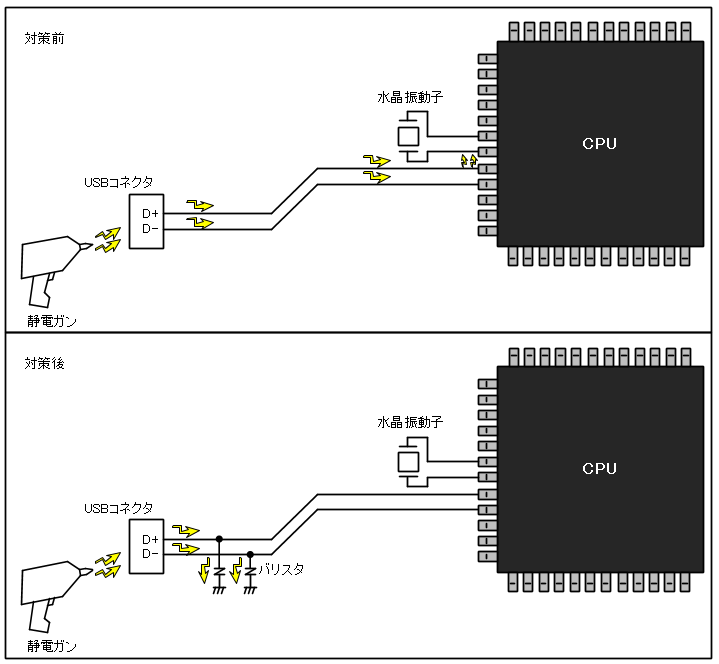

①USBケーブルへの間接放電で機器がフリーズ

[問題]

機器のUSBコネクタに接続したUSBケーブルへ気中放電を行った際、USBコネクタの金属シャーシに静電気が飛び込み、機器がフリーズして動作不能となった。

[原因]

フリーズの原因は以下の通りです。

①USBのデータ(+/-)に静電気が流入し、プロセッサのUSBデータポートまで到達。

②プロセッサのUSBデータポート隣にシステムクロック入力ポートがあり、このポートに静電気が飛び込む。

③プロセッサのシステムクロック入力ポートにクリスタルユニット(水晶振動子)を接続し、プロセッサ内部発振回路を使用していたが、飛び込んだ静電気とクロックが結合することでクロックが乱れ、フリーズとなった。

[対策]

この時は、原因の特定まで結構時間が掛かりました。

対策として、以下の2種類があり、コストを考えて①を採用しました。

①USDデータ信号(+/-)とGND間にバリスタを追加し、静電気をUSBコネクタの根本でGNDに逃がす。

②水晶振動子を水晶発振器に変更。発振回路を外部デバイスにすることで、静電気の影響を排除する。

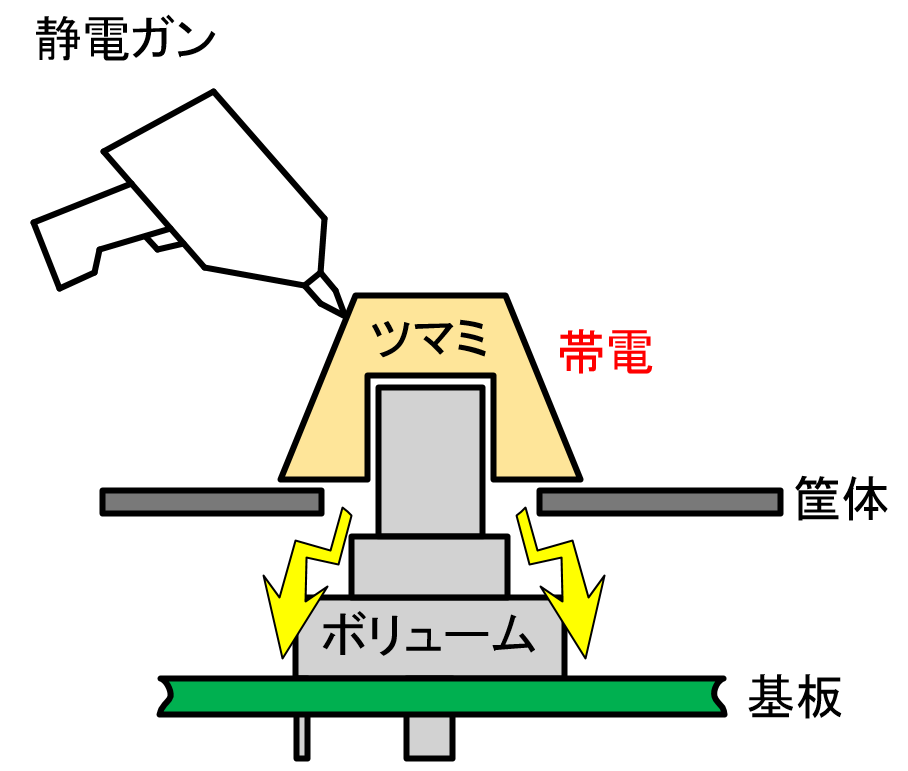

②機器のボリュームツマミに直接放電し機器がフリーズ

[問題]

メッキ加工を施したボリュームツマミに直接放電を行い、印加10回に到達する前に機器がフリーズして動作不能となった。

[原因]

メッキ加工を行ったツマミは金属のため直接放電試験を行ったが、このツマミは機器のGNDと導通がなく浮遊導体となっていたため、静電気の逃げ場がなく、溜まりに溜まって、距離が離れている内部基板まで飛び込みフリーズとなった。

[対策]

対策として、以下の2種類があり、実現性を考慮し①を採用しました。

①メッキ加工がツマミの裏側まで施されており、メッキ部と基板間距離を稼ぐため、ツマミの裏側をマスキングし、メッキ加工を表側だけとした。

②メッキ部と機器の金属部分を導電性材料で接触させ、静電気の逃げるルートを作る。ただし、ツマミは可動部品であり、常に導通を確保することが非常に困難。

これまでの経験上、機器を制御するプロセッサが実装された基板が4層以上の多層基板では、静電気による問題はあまり発生しません。

これは、内層をGND専用にできるため、GDNプレーンのインピーダンスが低くなり、ESDがGNDに流入してもESDによるGNDの揺れを大幅に低減することができるためです。

しかし、コストを優先させるあまり、プロセッサを実装する基板を2層基板とした場合、GNDのインピーダンスが高く、ESDの影響によるGNDバウンスが非常に大きく、これによりフリーズが多発し、逆に対策によるコストが上がる上、対策に非常に時間を要してしまいます。

よって、静電気の問題を起こしたくなければ、4層以上の基板を強く推奨します。

別の機会に、両面基板の設計について取り上げたいと思います。

両面基板のESD、まじで苦労しました…